- 2020-08-17 11:12:07

-

点击下载

全志F1C200S规格书,F1C200S PDF,F1C200S Datasheet,全志MP5主芯片规格书,视频播放器主芯片,MP4主芯片方案,最新MP4解码芯片,数码相框主芯片,数码相框解码主控,广告机解码芯片,单机版广告机解码芯片。

视频解码

图片解码

音频解码

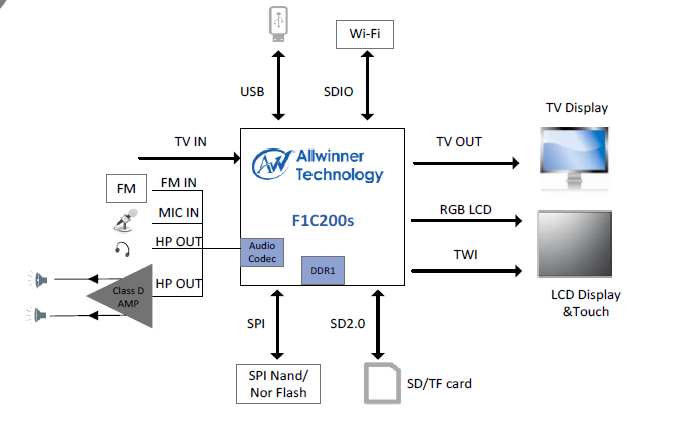

TheF1C200sprocessorrepresentsAllwinner’slatestachievementinmobileapplicationsprocessors.The processor targetstheneeds ofvideoboomboxmarkets.

TheF1C200sisbasedontheARM9CPUarchitecturewithahighdegreeoffunctionalintegration,andsupports

FullHDvideoplayback,includingH.264,H.263,MPEG1/2/4decoder.IntegratedaudiocodecandI2S/PCMinterface

provideenduserswithagoodaudioexperience.TV-INinterfaceenablesvideoinputbyconnectingtovideo

devices suchascamera,andTV-OUT interfaceenables video output by connecting toTV devices.

ToreducetheBOMcosts,theF1C200sbuilt-inDDR1memory,anditispackedwithgeneral-purposeperipherals

suchasUSBOTG,UART,SPI,TWI,TP,SD/MMC,CSIetc.TheF1C200soutperformscompetitorsinermsofits

powerful performance,lowpowerconsumption,andflexiblescalability.

Applications:

●VideoPlayback

●AudioPlayback

●FM

2.1. CPU Architecture

The F1C200s platform is based on ARM9 CPU architecture.

● Five-stage pipeline architecture

● Support 16KByte D-Cache

● Support 32KByte I-Cache

2.2. Memory Subsystem

This section consists of internal memory and external memory:

● Boot ROM

● SDRAM

● SD/MMC Interface

Boot ROM

● Internal memory

● On-Chip ROM boot loader

● Support system boot from SPI Nor/Nand Flash, and SD/TF card

● Support system code download through USB OTG

SDRAM

● SIP DDR1

SD/MMC Interface

● External memory

● Support secure digital memory protocol commands (up to SD2.0)

● Support secure digital I/O protocol commands (up to SDIO2.0)

● Support multimedia card protocol commands (up to eMMC4.41)

● Support one SD (Verson1.0 to 2.0) or MMC (version 3.3 to eMMC4.41)

● Support hardware CRC generation and error detection

● Support host pull-up control

● Support SDIO interrupts in 1-bit and 4-bit modes

● Support SDIO suspend and resume operation

● Support SDIO read wait

● Support block size of 1 to 65535 bytes

● Support descriptor-based internal DMA controller

● Internal 128 bytes FIFO for data transfer

● Support 3.3V IO pad

2.3. System Peripheral

This section includes:

● Timer

● INTC

● CCU

● DMA

● PWM

Timer

● Three timers

● Support watchdog reset

● Support audio and video synchronize counter

INTC

● Support up to 64 interrupts

● Support 4-level priority

● Support interrupt mask

● Support interrupt fast forcing

● Support one external interrupt

CCU

● Support 6 PLLs

● Control of clock generation, division, distribution and gating

● Control of device software reset

DMA

● Support Normal DMA and Dedicated DMA

● Support two kinds of interrupt

● Support hardware continuous transfer mode

PWM

● Support two PWM outputs

● Support cycle mode and pulse mode

● Support 24MHz maximum output frequency

2.4. Display Subsystem

This section includes:

● Display Engine

● Display Output

Display Engine

● Support four layers overlay, each layer size up to 2048x2048 pixels

● Support Alpha blending / color key

● Support multi-format input formats

n 1/2/4/8/16/32 bpp color

n YUV444/YUV422/YUV420/YUV411

● Support hardware cursor

● Support scaling function for one layer

n ARGB8888/YUV444/YUV420/YUV422/YUV411

n Input and output size up to 1280x720 pixels

n Resize ratio from 1/16X to 32X

n 4-tap 32-phase anti-aliasing filter in horizontal and vertical direction

n Scaler supports write-back to memory function

Display Output

● LCD RGB interface, TTL interface, up to 1280x720@60fps

● LCD Serial RGB interface, CCIR656 interface, up to 720x576@60fps

● LCD i8080 interface with 18/16/9/8 bit, up to 800x480@60fps

● LCD Dither function, support RGB666/RGB565 interface

● TV CVBS output, support NTSC/PAL, with auto plug detecting

2.5. Video Engine

● Support H.264 BP/MP/HP up to 1280x720@30fps decoding

● Support format MPEG1 and MPEG2 up to 1280x720@30fps decoding

● Support format MPEG4 SP/ASP GMC and H.263 including Sorenson Spark up to 1280x720@30fps decoding

● Support MJPEG encode up to 1280x720@30fps

● Support JPEG encode size up to 8192 x 8192

● Support JPEG decode size up to 16384 x 16384

2.6. Image Subsystem

This section includes:

● CSI

● CVBS Input

CSI

● Support 8-bit CMOS-sensor interface

● Support YUV camera up to 5Mega pixel

● Support CCIR656 protocol for NTSC and PAL

CVBS Input

● Support NTSC/PAL

● Support 3D comb filter

● Support two TV CVBS channels:TVIN0,TVIN1

2.7. Audio Subsystem

Audio Codec

● Two audio digital-to-analog(DAC) channels

● Stereo capless headphone drivers:

n Up to 100dB DR

n Supports DAC Sample Rates from 8KHz to 192KHz

● Support analog/ digital volume control

● Analog low-power loop from FM/ line-in /microphone to headphone outputs

● Three audio inputs:

n One microphone input

n Stereo FM left/right input

n One Line-in input

● One audio analog-to-digital(ADC) channel

n 96dB SNR@A-weight

n Supports ADC Sample Rates from 8KHz to 48KHz

n Support Auto Gain Control(AGC)

2.8. System Peripherals

This section includes:

● USB 2.0 OTG

● KEYADC

● TP

● Digital Audio Interface

● UART

● SPI

● TWI

● IR

● RSBTM

● OWA

USB 2.0 OTG

● Support AMBA AHB Slave mode

● Support the Host Negotiation Protocol (HNP) and the Session Request Protocol (SRP)

● Support the UTMI+ Level 3 interface . The 8-bit bidirectional data buses are used.

● 64-Byte Endpoint 0 for Control Transfer (Endpoint0)

● Support High-Bandwidth Isochronous & Interrupt transfers

● Automated splitting/combining of packets for Bulk transfers

● Support point-to-point and point-to-multipoint transfer in both Host and Peripheral mode

● Include automatic ping capabilities

● Soft connect/disconnect function

● Perform all transaction scheduling in hardware

● Power Optimization and Power Management capabilities

● Include interface to an external Dedicated Central DMA controller. Data is transferred through Special bus for saving AHB bus bandwidth

● Support industry-standard single port SRAM for USB Configurable Data FIFO. The size is 2048 byte with 32-bit word width. The RAM can be used by other modules when USB OTG disable

- 上一篇 [返回首页] [打印] [返回上页] 下一篇

联系我们

联系人:

钟先生(业务、定制开发)电话:

13684930796传真:

0755-29495182邮箱:

dvbest@126.com